更多“试用一片38线译码器74LS138和两个4输入与非门组成一位…”相关的问题

更多“试用一片38线译码器74LS138和两个4输入与非门组成一位…”相关的问题

第2题

试分别用下列方法设计全加器。 (1) 用与非门; (2) 用或非门; (3) 用双4选1数据选择器74LS153; (4) 用3线

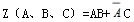

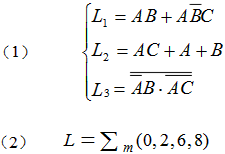

试分别用下列方法设计全加器。

(1) 用与非门;

(2) 用或非门;

(3) 用双4选1数据选择器74LS153;

(4) 用3线-8线译码器74LS138和与非门。

第3题

试用一片集成四位二进制加法计数器74LS161和一片3/8线译码器74LS138组成一个五节拍顺序脉冲发生器。

试用一片集成四位二进制加法计数器74LS161和一片3/8线译码器74LS138组成一个五节拍顺序脉冲发生器。

第6题

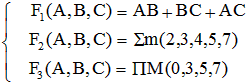

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位进位为Ci。

第9题

试用4片1024×4位的RAM和3线-8线译码器74LS138组成4096×4位的RAM。

试用4片1024×4位的RAM和3线-8线译码器74LS138组成4096×4位的RAM。

如果结果不匹配,请

如果结果不匹配,请