题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图12.29所示是两个4线-2线二进制编码器,试写出它们的F2和F1的逻辑表达式。列出真值表,并比较两者有何不同。

图12.29所示是两个4线-2线二进制编码器,试写出它们的F2和F1的逻辑表达式。列出真值表,并比较两者有何不同。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图12.29所示是两个4线-2线二进制编码器,试写出它们的F2和F1的逻辑表达式。列出真值表,并比较两者有何不同。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图12.29所示是两个4线-2线二进制编码器,试写出它们的F…”相关的问题

更多“图12.29所示是两个4线-2线二进制编码器,试写出它们的F…”相关的问题

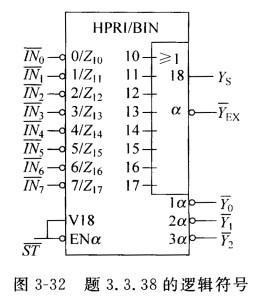

图3—32所示是8线-3线优先编码器74148的逻辑符号,其功能表如表3-5所示。试用以构成一个16线-4线优先编码器。

试设计一个4/2线二进制编码器,输入信号为 ,低电平有效。输出的二进制代码用Y1,Y0表示。

,低电平有效。输出的二进制代码用Y1,Y0表示。

试用一片图3.2.36所示4线—16线译码器74LS154及最少的门电路实现两个二位二进制数A1A0、B1B0的大小比较电路,即A>B时,F1=1;A<B时,F2=1;A=B时,F3=1。74LS154的

(1)列出真值表。

(2)列出电路输出函数F1、F2、F3的表达式。

(3)画出其接线图。

试画出在表2-24中说明的4线-2线优先编码器的卡诺图,并写出逻辑表达式。

表2-24 4线-2线优先编码器真值表

|

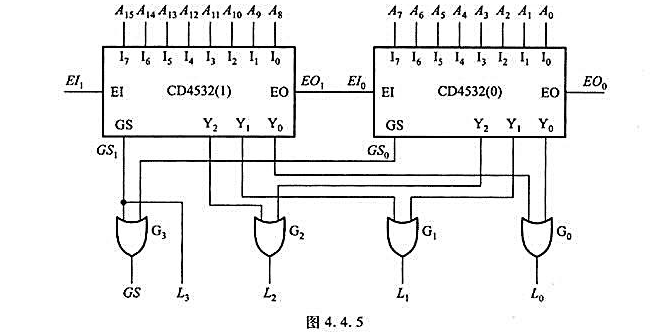

(1)首先根据8线-3线优先编码器CD4532的功能表,写出该编码器的行为级描述,并用QuartusII软件对该模块进行逻辑功能仿真,并给出仿真波形。

(2)然后调用上面设计的编码器子模块和基本门级元件,完成16线-4线优先编码器的建模。

(3)最后用QuartusII软件对整个电路进行逻辑功能仿真,并给出仿真波形。

图1中所示是8线-3线优先编码器74148的逻辑符号,其功能表如表3-5所示。试用以构成一个16线-4线优先编码器。

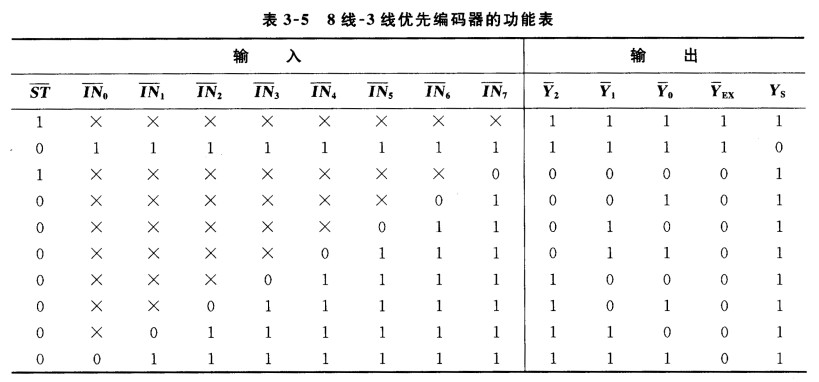

表3-5 8线-3线优先编码器的功能表

|

设计1个4线-2线优先编码器,要求输入、输出均为高电平有效,试写出用与非门实现的编码器输出的逻辑表达式。

试用3线-8线译码器和8线-3线优先编码器构成y=(3x)mod8电路,x和y都是三位二进制数。8线-3线优先编码器的逻辑符号如图所示。