更多“设计一个将余3码变换为8421BCD码的组合逻辑电路。”相关的问题

更多“设计一个将余3码变换为8421BCD码的组合逻辑电路。”相关的问题

第5题

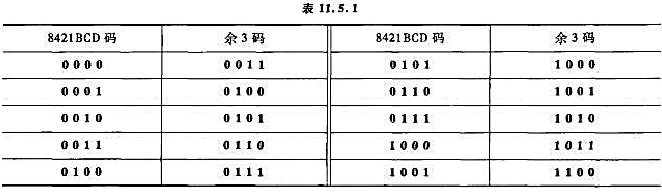

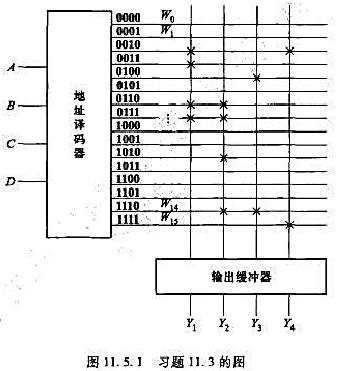

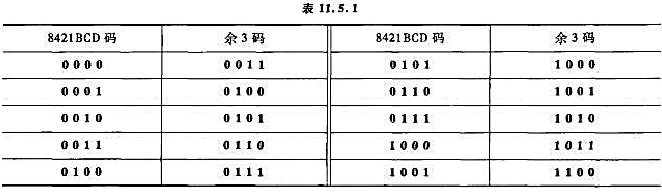

试用ROM设计一个8421BCD码转换成余3码的代码转换器。已知代码转换真值表见表11.5.1,试画出代码

转换阵列图。

点击查看答案

答:

2、试用ROM设计一个8421BCD码转换成余3码的代码转换器。已知代码转换真值表见表11.5.1,试画出代码转换阵列图。

第9题

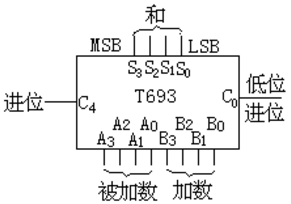

设计一个8421BCD码→余3码换码电路。要求: (1)用ROM实现; (2)用FPLA实现; (3)用译码器芯片实现; (4)用全

设计一个8421BCD码→余3码换码电路。要求:

点击查看答案

(1)用ROM实现;

(2)用FPLA实现;

(3)用译码器芯片实现;

(4)用全加器实现;

注意:必要时可加门电路。

如果结果不匹配,请

如果结果不匹配,请