更多“集成四位同步二进制加法计数器74161有四个数据输入端D0―…”相关的问题

更多“集成四位同步二进制加法计数器74161有四个数据输入端D0―…”相关的问题

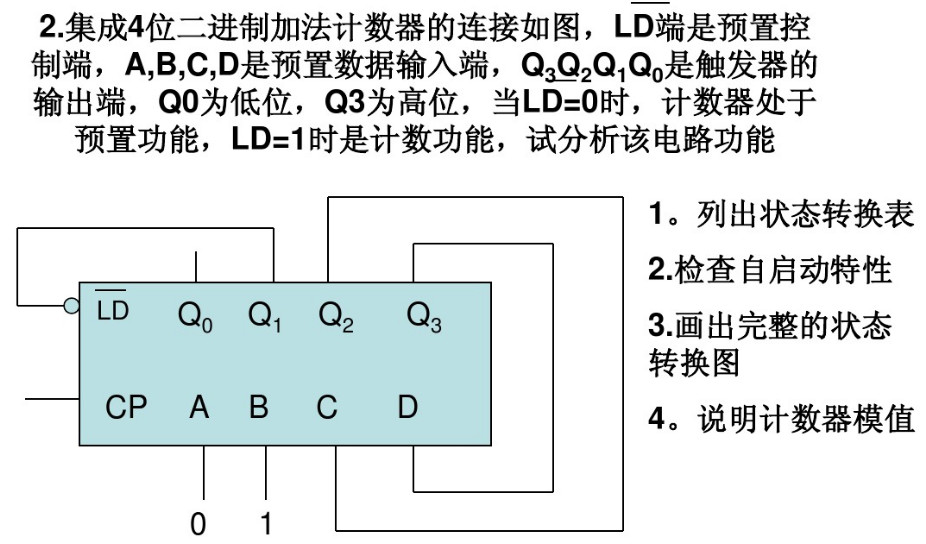

第1题

中规模集成同步4位二进制加法计数器74LS161的功能表如附表所示,要求:将两片74LS161用预置数法构成从0开始的

81进制计数器,画出电路接线图。

| CP | bar{CR}bar{LD} | CTPCTT | D0D1D2D3 | Q0n+1 | Q1n+1 | Q2n+1 | Q3n+1 |

| × | 0 × | × × | × × × × | 0 | 0 | 0 | 0 |

| ↑ | 1 0 | × × | d0d1d2d3 | d0 | d1 | d2 | d3 |

| × | 1 1 | 0 × | × × × × | 保 持 | |||

| × | 1 1 | × 0 | × × × × | 保 持 | |||

| ↑ | 1 1 | 1 1 | × × × × | 4位二进制加法计数器 进位输出:CO=CTTQ3Q2Q1Q0 | |||

第2题

逻辑分析题 4位同步二进制计数器74161的功能表如表所示,Q3为高位输出,C为与时钟同步的进位输出,进入1111状

逻辑分析题

4位同步二进制计数器74161的功能表如表所示,Q3为高位输出,C为与时钟同步的进位输出,进入1111状态且ENT=1时,由C端输出一个周期的正脉冲。

| CP | R_{bar{D}} | bar{LD} | ENP | ENT | Q3 | Q2 | Q1 | Q0 |

| varphi | 0 | varphi | varphi | varphi | 0 | 0 | 0 | 0 |

| ↑ | 1 | 0 | varphi | varphi | D3 | D2 | D1 | D0 |

| varphi | 1 | 1 | 0 | 1 | 保持 | |||

| varphi | 1 | 1 | varphi | 0 | 保持(但C=0) | |||

| ↑ | 1 | 1 | 1 | 1 | 加法计数 |

第3题

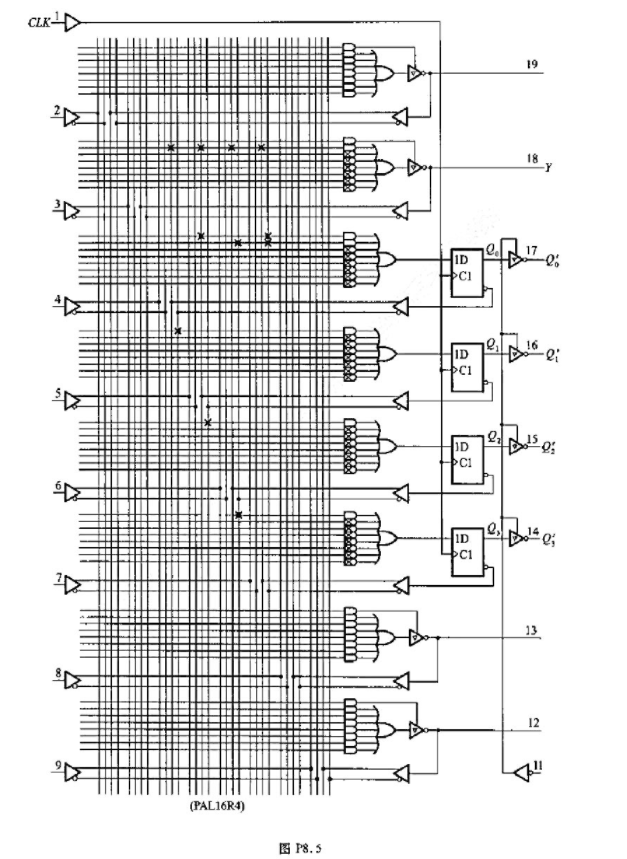

用PALl6R4设计一个4位二进制可控计数器.要求在控制信号M1M0=11时作加法计数;在M1M

0=10时为预置数状态(时钟信号到达时将输入数据D3、D2、D1、D0并行置人4个触发器中);M1M0=01时为保持状态(时钟信号到达时所有的触发器保持状态不变);M1M0=00时为复位状态(时钟信号到达时所有的触发器同时被置1).此外,还应给出进位输出信号.PALI6R4的电路图见图P8.5.

点击查看答案

第6题

中规模集成同步4位二进制加法计数器74LS161的功能表如下表所示,要求: CP bar{CR} bar{LD} CTP

中规模集成同步4位二进制加法计数器74LS161的功能表如下表所示,要求:

| CP | bar{CR}bar{LD} | CTPCTT | D0D1D2D3 | Q0n+1Q1n+1Q2n+1Q3n+1 |

| × | 0 × | × × | × × × × | 0 0 0 0 |

| ↑ | 1 0 | × × | d0d1d2d3 | d0d1d2d3 |

| × | 1 1 | 0 × | × × × × | 保 持 |

| × | 1 1 | × 0 | × × × × | 保 持 |

| ↑ | 1 1 | 1 1 | × × × × | 4位二进制加法计数器 进位输出:CO=CTTQ3Q2Q1Q0 |

第7题

中规模集成同步4位二进制加法计数器74LS161的功能表如下表所示,其简化逻辑符号如题八图所示,要求:

| bar{CR} | bar{LD} | CTPCTT | CP | D0D1D2D3 | Q0n+1Q1n+1Q2n+1Q3n+1 |

| 0 1 1 1 1 | × 0 1 1 1 | × × × × 1 1 0 × × 0 | × ↑ ↑ × × | ×××× d0d1d2d3 ×××× ×××× ×××× | 0 0 0 0 d0d1d2d3 4位二进制加法计数器 保 持 保 持 |

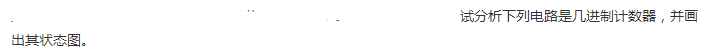

第8题

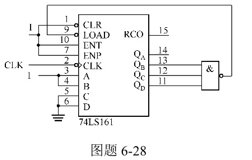

图题6-28所示为具有同步预置功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该

图题6-28所示为具有同步预置功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

第9题

对于中规模集成计数器74LS161,以下哪些选项是正确的()。

A.时钟动作沿是上升沿

B.时钟动作沿是下降沿

C.预置数方式为同步数据置入

D.异步复位端为低电平有效

E.引脚9为并行输入控制端

第10题

图题6-27所示为具有同步预置功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该

图题6-27所示为具有同步预置功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

第11题

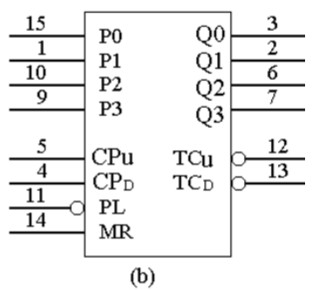

74LS192型同步十进制可逆计数器的功能表和逻辑符号分别如表21.3和图 21.16所示。所谓可逆,就是能进行加法计

数和减法计数。(1)说明表中各项的意义;(2)试用两片74LS192型计数器构成百进制计数器。先将各片接成十进制加法计数工作状态,而后连接两片。图中

分别为进位和借位输出端。

分别为进位和借位输出端。

表21.3 | |||||

输入 | 输出 | ||||

RD | overline{LD} | CP+ | CP- | A3A2A1A0 | Q3Q2Q1Q0 |

0 0 | 0 1 | × ↑ | × 1 | d3d2d1d0 × | d3d2d1d0 加法计数 |

0 0 1 | 1 1 × | 1 1 × | ↑ 1 × | × × × | 减法计数 保持 0 0 0 0 |

如果结果不匹配,请

如果结果不匹配,请