题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

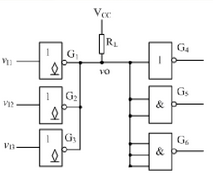

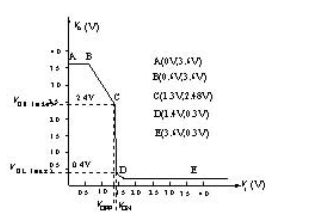

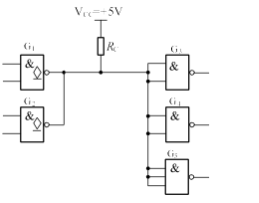

图2.4.5中G1、G2为OC门,G3、G4、G5为TTL门电路,设OC门最大灌电流IOL=14mA,最大拉电流IOH=0.25mA,与非门输入短

图2.4.5中G1、G2为OC门,G3、G4、G5为TTL门电路,设OC门最大灌电流IOL=14mA,最大拉电流IOH=0.25mA,与非门输入短路电流IIL=1.6mA,高电平输入电流IIH=0.05mA,求上拉电阻RP的取值范围(要求VOH≥3V,VOL≤0.3V)。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图2.4.5中G1、G2为OC门,G3、G4、G5为TTL门…”相关的问题

更多“图2.4.5中G1、G2为OC门,G3、G4、G5为TTL门…”相关的问题