题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

S7-200有三种普通计数器,其中()具有加计数和减计数两个输入端,通过获取对应计数输入信号的上升沿,进行加法、减法计数。

A.加计数器(CTU)

B.减计数器(CTD)

C.可逆计数器(CTUD)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.加计数器(CTU)

B.减计数器(CTD)

C.可逆计数器(CTUD)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“S7-200有三种普通计数器,其中()具有加计数和减计数两个…”相关的问题

更多“S7-200有三种普通计数器,其中()具有加计数和减计数两个…”相关的问题

A.置输入信号UP/DN=0,则为加1计数;

B.置输入信号UP/DN=0,则为减1计数;

C.Rco仅为进位信号;

D.计数器不能用跳跃的方法实现任意模数的计数。

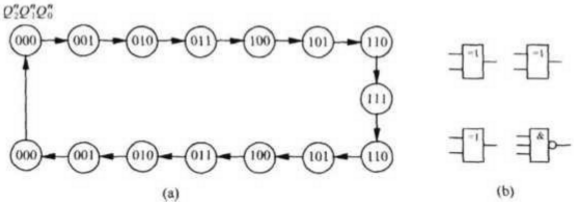

用集成电路芯片74LS161设计一个计数器,自动完成3位二进制加/减循环计数,状态转换图如图T9.4-1(a)所示,要求只能用三个2输入异或门和一个3输入与非门实现,如图T9.4-1(b)所示。

提示:将74LS161的输出作为输入变量,3位二进制加/减循环计数器的状态作为输出变量,列出状态转换真值表,其中状态1000不用,并用端作为加/减转换控制。

A.输入端有脉冲上升沿时,计数器启动,从当前值 0 开始加 1 计数,一个脉冲上升沿加一次,直到最大值 32767 时停止计数

B.当前值等于或大于设定值时,计数器“ ON ”,当前值仍继续累计脉冲数

C.计数器“ ON ”时,其常闭触点断开,常开触点闭合

D.复位输入端接通或计数器执行复位指令时,计数器被复位“ OFF ”,当前值变 0

CT4193是2~16进制可预置同步可逆计数器。其逻辑符号如图所示。CT4193具有双时钟CP+、CP-。加法计数时,从CP+输入计数脉冲,CP-=1;减法计数时,从CP一输入计数脉冲,CP+=1。CR是清零端,正脉冲有效,LD是预置端,低电平有效。C0为进位输出端,B0为借位输出端,它们都输出负脉冲。

试用CT4193,采用异步预置法组成十进制减法计数器。

用PAL16R6设计一个4位二进制计数器,要求:

(1)具有并行置数功能。并行数据输入为P0,P1,P2,P3,控制信号为。当

时并行置数;当

时计数。

(2)具有加/减计数功能。控制信号为,当

且

时为加计数;当

且

时为减计数。

(3)具有并行输出Q0,Q1,Q2,Q3。

(4)具有进位输出C和借位输出B。

用JK触发器设计具有以下特点的计数器:

(1)计数器有两个控制输入C1和C2,C1用以控制计数器的模数,C2用以控制计数的增减;

(2)若C1=0计数器的M=3;如果C1=1,则计数器为M=4;

(3)若C2=0,则为加法计数,若C2=1,则为减法计数。作出状态表,并画出计数器逻辑图。