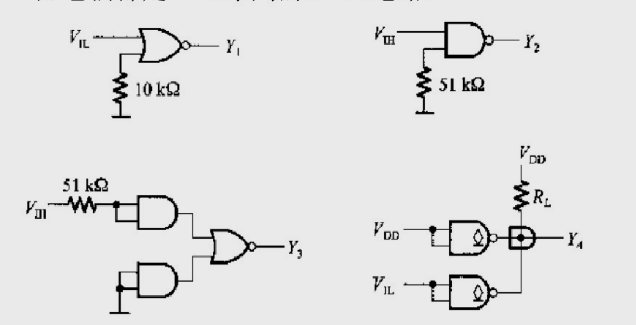

更多“说明图3.15中各门电路的输出是高电平还是低电平。已知它们都…”相关的问题

更多“说明图3.15中各门电路的输出是高电平还是低电平。已知它们都…”相关的问题

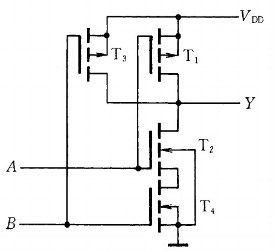

指出图3.14中各门电路的输出是什么状态(高电平、低电平或高阻态)。已知这些门都是74系列TTL电路。

简答:已知图2.2.3各电路都是TTL门,试简述各门电路的输出是什么状态(高电平、低电平或高阻态),要求写出表达式。

计算图3.27所示电路中接口电路输出端vC的高、低电平,并说明接口电路参数的选择是否合理。三极管的β=40,VCE(sat)=0.1V,RCE(sat)=20Ω。CMOS或非门的电源电压VDD=5V,空载输出的高、低电平分别为VOH=4.95V,VOL=0.05V,门电路的输出电阻小于200Ω,高电平输出电流的最大值和低电平输出电流的最大值均为4mA。TTL或非门的高电平输入电流IIH=40μA,低电平输入电流IIL=-1.6mA。

如图题2.6所示的门电路均为TTL门电路,试指出各门电路的输出是什么状态(高电平、低电平或高阻态)。

图P3.6是用输出端并联的OD门驱动CMOS反相器和与非门的电路。试计算当VDD=5V时外接电阻RP阻值的合理范围。要求OD门输出的高、低电平满足VOH≥3.5V、VOL≤0.3V。已知OD门G1~G3输出高电平时,每个输出端MOS管的漏电流为IOH(max)=10μA;输出低电平时,每个输出端MOS管输出电流的最大值为IOL(max)=4mA,输出低电平VOL≤0.3V。CMOS反相器和与非门每个输入端的高电平输入电流和低电平输入电流最大值均为1μA。

在图3.24所示电路中,已知G1和G2为74LS系列OC输出结构的与非门,输出管截止时的漏电流最大值为IOH(max)=100μA,低电平输出电流最大值为IOL(max)=8mA,这时输出的低电平为VOL(max)=0.4V。G3~G6是74LS系列的或非门,它们高电平输入电流最大值为IIH(max)=20μA,低电平输入电流最大值为IIL(max)=-0.4mA。给定VCC=5V,要求满足VOH≥3.4V、VOL≤0.4V,试求RL取值的允许范围。

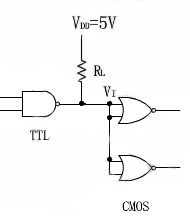

图3.28是用TTL电路驱动CMOS电路的实例,试计算上拉电阻RL的取值范围。TTL与非门在VOL≤0.3V时的最大输出电流为8mA,输出端的T5管截止时有50μA的漏电流。CMOS或非门的高电平输入电流和低电平输入电流的最大值均为1μA。要求加到CMOS或非门输入端的电压满足VIH≥4V,VIL≤0.3V。给定电源电压VDD=5V。

如果结果不匹配,请

如果结果不匹配,请