题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

某计数器中3个触发器输出端Q0、Q1Q2的输出信号波形如图5.4.2所示,由波形图可知该计数器是________

________进制计数器。

.jpg)

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

.jpg)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“某计数器中3个触发器输出端Q0、Q1Q2的输出信号波形如图5…”相关的问题

更多“某计数器中3个触发器输出端Q0、Q1Q2的输出信号波形如图5…”相关的问题

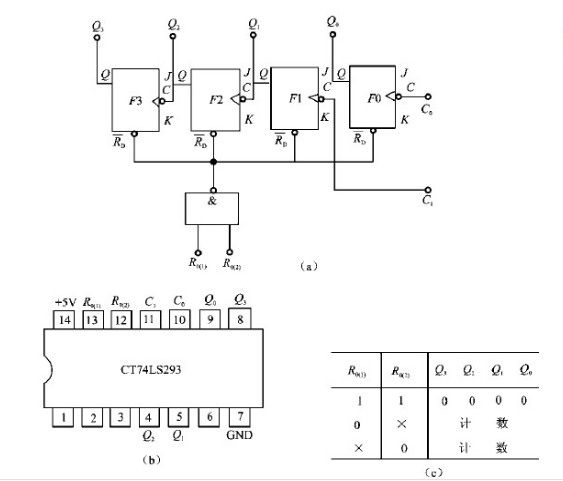

74LS293型计数器的逻辑图,外引线排列图及功能表如图21.45所示。它有两个时钟脉冲输入端CP0和CP1。试问:(1)从CP0输入,Q0输出时,是几进制计数器?(2)从CP1输入,Q3,Q2,Q1输出时,是几进制计数器?(3)将Q0端接到CP1端,从CP0输入,Q3,Q2,Q1,Q0输出时,是几进制计数器?图中R0(1)和R0(2),是清零输入端,当该两端全为1时,将4个触发器清零。

1.jpg)