题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

计数器指令CNT有两个输入端,其中CP为()端,R为()端。

计数器指令CNT有两个输入端,其中CP为()端,R为()端。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“计数器指令CNT有两个输入端,其中CP为()端,R为()端。”相关的问题

更多“计数器指令CNT有两个输入端,其中CP为()端,R为()端。”相关的问题

1.jpg) 试求一个Z脉冲周期内应包含多少个CP脉冲周期。

试求一个Z脉冲周期内应包含多少个CP脉冲周期。

2.jpg)

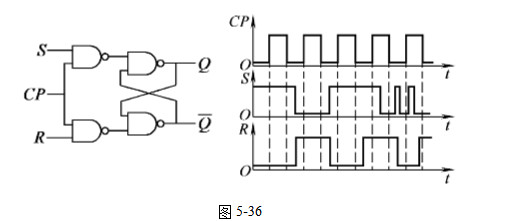

设同步RS触发器的初始状态为Q=0,R、S端和CP端的输入信号波形如图(a)所示,画出相应的Q、 端的波形。

端的波形。

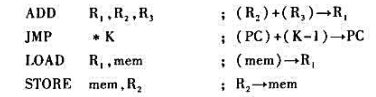

写出控制器执行上述指令的微操作及节拍安排。

1.jpg)