题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

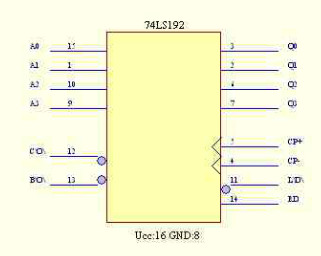

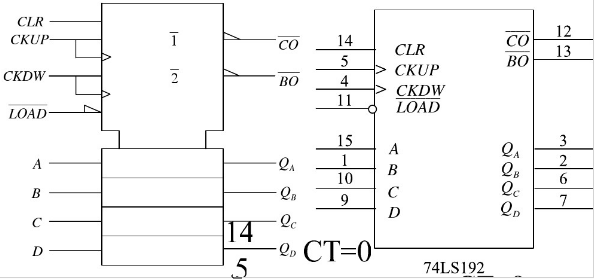

中规模时序电路分析设计 74LS192是十进制计数器,计数的编码采用8421码,计数循环是0000~1001,74LS192是采用

中规模时序电路分析设计

74LS192是十进制计数器,计数的编码采用8421码,计数循环是0000~1001,74LS192是采用双时钟方式的可逆计数器。 是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是

是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是 ,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

| 74LS192的逻辑功能表 | |||||||||||

| CKUP | CKDW | bar{LOAD} | CLR | D | C | B | A | QD | QC | QB | QA |

| varphi | varphi | varphi | 1 | varphi | varphi | varphi | varphi | 0 | 0 | 0 | 0 |

| varphi | varphi | 0 | 0 | d | c | b | a | d | c | b | a |

| ↑ | 1 | 1 | 0 | varphi | varphi | varphi | varphi | 加计数 | |||

| 1 | ↑ | 1 | 0 | varphi | varphi | varphi | varphi | 减计数 | |||

| 1 | 1 | 1 | 0 | varphi | varphi | varphi | varphi | 保持原状态 |

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“中规模时序电路分析设计 74LS192是十进制计数器,计数的…”相关的问题

更多“中规模时序电路分析设计 74LS192是十进制计数器,计数的…”相关的问题

分别为进位和借位输出端。

分别为进位和借位输出端。