题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

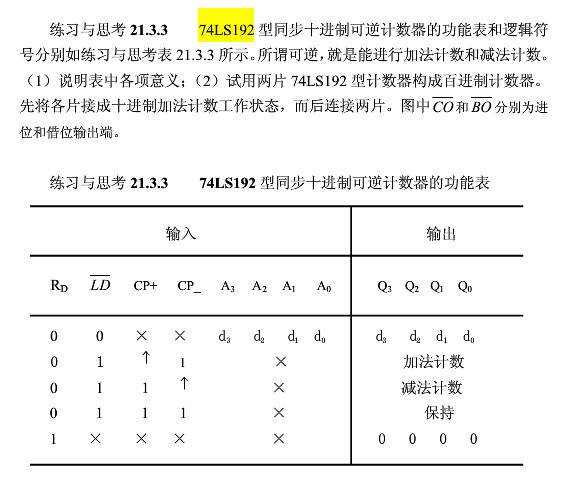

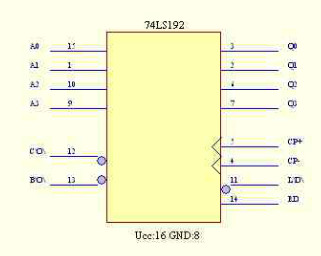

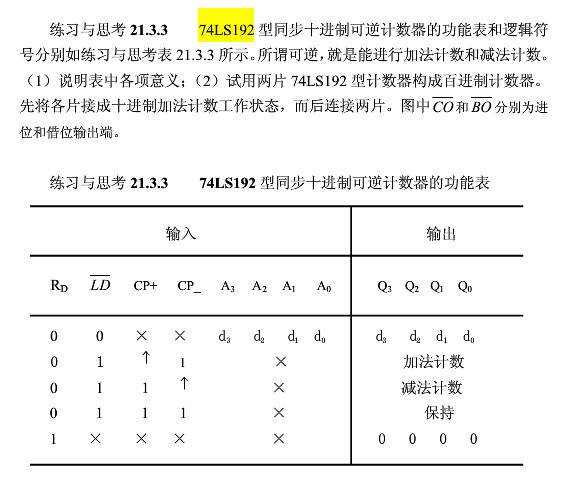

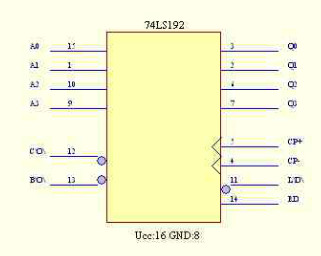

74LS192型同步十进制可逆计数器的功能表和逻辑符号分别如表21-4和图21-7所示。所谓可逆,就是能进行加法计数

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“74LS192型同步十进制可逆计数器的功能表和逻辑符号分别如…”相关的问题

更多“74LS192型同步十进制可逆计数器的功能表和逻辑符号分别如…”相关的问题

数和减法计数。(1)说明表中各项的意义;(2)试用两片74LS192型计数器构成百进制计数器。先将各片接成十进制加法计数工作状态,而后连接两片。图中

分别为进位和借位输出端。

分别为进位和借位输出端。

输入

输出

RD

overline{LD}

CP+

CP-

A3A2A1A0

Q3Q2Q1Q0

0

0

0

1

×

↑

×

1

d3d2d1d0

×

d3d2d1d0

加法计数

0

0

1

1

1

×

1

1

×

↑

1

×

×

×

×

减法计数

保持

0 0 0 0

中规模时序电路分析设计

74LS192是十进制计数器,计数的编码采用8421码,计数循环是0000~1001,74LS192是采用双时钟方式的可逆计数器。 是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是

是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是 ,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

用同步二进制加法计数器74161(逻辑符号及功能表见附录)和一个3-8线译码器74138以及门电路设计一个具有开机消零功能的模7计数器,要求计数器按下列规律计数,要求写出设计过程,画出电路图:

0,4,9,12,3,6,9,0,4,…

试用CT4193,采用异步预置法组成十进制减法计数器。

用同步时序电路设计一模6 的可逆计数器,当控制端X为1时,计数器做减法计数,当X为0时,计数器做加法计数(触发器用JK触发器)。