题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

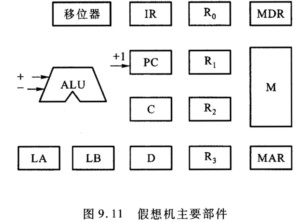

某假想机主要部件如图9.11所示,其中: LA ALU的A输入端选择器 LB ALU的B输

(1)补充各种部件之间的主要连接线,并注明数据流动方向。 (2)写出ADD @R1,@R2和SUB @R1,@R2指令取指阶段和执行阶段的信息流程。R1寄存器中存放源操作数的地址,R2寄存器中存放的是目的操作数的地址。

(1)补充各种部件之间的主要连接线,并注明数据流动方向。 (2)写出ADD @R1,@R2和SUB @R1,@R2指令取指阶段和执行阶段的信息流程。R1寄存器中存放源操作数的地址,R2寄存器中存放的是目的操作数的地址。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

(1)补充各种部件之间的主要连接线,并注明数据流动方向。 (2)写出ADD @R1,@R2和SUB @R1,@R2指令取指阶段和执行阶段的信息流程。R1寄存器中存放源操作数的地址,R2寄存器中存放的是目的操作数的地址。

(1)补充各种部件之间的主要连接线,并注明数据流动方向。 (2)写出ADD @R1,@R2和SUB @R1,@R2指令取指阶段和执行阶段的信息流程。R1寄存器中存放源操作数的地址,R2寄存器中存放的是目的操作数的地址。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“某假想机主要部件如图9.11所示,其中: LA ALU的A输…”相关的问题

更多“某假想机主要部件如图9.11所示,其中: LA ALU的A输…”相关的问题

某假想机主要部件如图9.11所示,其中:

LAIALU的A输入端选择器

LB ALU的B输入端选择器

M 主存

MDR 主存数据寄存器

IR指令寄存器

MAR主存地址寄存器

PC程序计数器

R0~R3通用寄存器

C、D暂存器

(1)补充各种部件之间的主要连接线,并注明数据流动方向。.

(2)写出ADD @R1,@R2和SUB @R1,@ R2指令取指阶段和执行阶段的信息流程。R1寄存器中存放源操作数的地址,R2寄存器中存放的是目的操作数的地址。

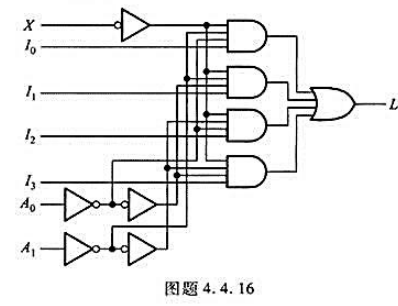

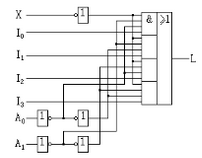

数据选择器如图题4.4.16所示,并行输入数据I3I2I1I0=1010,控制端X=0,A1A0的态序分别为00,01,10,11,试画出输出端L的波形。

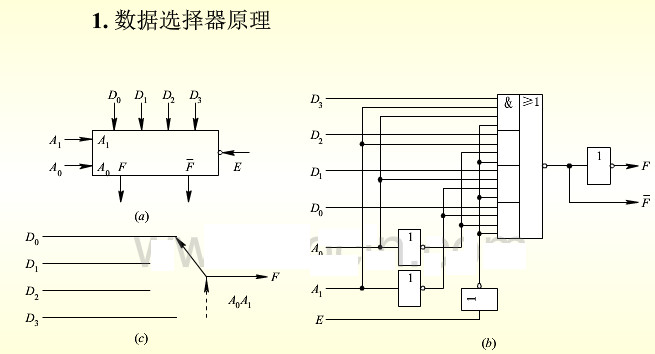

如图是一个4选1数据选择器的逻辑图,D0~D3是被选数据输入端,A1、A0是选择输入端,F是输出端。试写出输出的逻辑表达式和电路的逻辑状态表,并说明当A1,A0为00、01、10、11时,分别是哪一个数据从输出端输出。

数据选择器如下图所示,并行输入数据I3I2I1I0=1010,控制端X=0,A1A0的态序为00、01、10、11,试画出输出端L的波形。

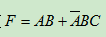

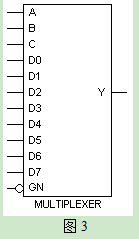

下图3所示为8-1多路选择器(A、B、C为选择输入端,A为高位,GN为允许端,低有效)。试用其实现逻辑函数 。可在图上直接连线,但要写出过程(如真值表,表达式等)。

。可在图上直接连线,但要写出过程(如真值表,表达式等)。

用图3.2.81所示的电路及一个四选一数据选择器实现逻辑函数F(A,B,C,D)=∑m(1,3,5,7,11,12,13,14)。要求只用A、B、C、D四个变量和图3.2.81中电路的输出端L、M及输出端N实现(既不能用“0”和“1”常量作为输入,也不能用A、B、C、D的反变量作为输入)。

4选1数据选择器的设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4选1数据选择器电路,建立4选1数据选择器的实验模式。通过电路仿真和硬件验证,进一步了解4选1数据选择器的功能。

设计原理

4选1数据选择器的元件符号如图所示,其中a、b、c和d是4位数据输入端;s1和s0是控制输入端;z是数据输出端。当s1s0=00时,输出z=a;s1s0=01时,z=b;s1s0=10时,z=c:s1s0=11时,z=d。